## Nationaal Lucht- en Ruimtevaartlaboratorium

National Aerospace Laboratory NLR

## **Executive summary**

## **Enhanced SAR data compressor for Sentinel-1**

### Problem area

The Sentinel-1 Earth Observation satellite requires high-performance on-board compression of it's Synthetic Aperture Radar (SAR) data stream. Conventional solutions, such as data reduction by Block Adaptive Quantization (BAQ) can not meet these requirements. This calls for a new approach using advanced space-qualified ASIC devices.

### **Description of work**

In this report a novel approach to the on-board compression of raw SAR data is presented, the so-called **Entropy-Constrained BAQ** (ECBAQ). It is more efficient than BAQ with respect to the resulting coding rate. Moreover, the compression performance of ECBAQ can be further improved when it is applied in the frequency domain. Using optimized twodimensional bit allocation with a carefully designed rate control loop in combination with efficient entropy coding, results in a design that is compatible with the multimode operations of the SAR onboard of Sentinel-1 and meets the image quality and data rate requirements.

### **Results and conclusions**

For the compression of raw data from multi-mode SAR instruments, **Entropy Constrained Block** Adaptive Quantization is an attractive option. In the time domain the compression results exceed that of BAQ by more than 20 %. Moreover, in a frequencydomain configuration, the average compression ratio is more than twice that of BAQ with the same image quality. The implementation on-board satellites is feasible due to the availability of the PowerFFT, a very fast FFT-oriented DSP ASIC, which is currently being spacequalified.

### **Applicability**

The presented compression method is an attractive compression method for application on all future SAR satellites.

### Report no.

NLR-TP-2007-414

### Author(s)

T. Algra L. Bierens

### **Report classification**

**UNCLASSIFIED**

#### Date

November 2007

## **Knowledge area(s)**

Geomatics Space Methods for Development and Qualification of Avionics

### Descriptor(s)

SAR Compression Satellite FFT

This report is based on a presentation held on the DASIA 2007 (DAta Systems in Aerospace) Conference, Naples, 29 May - 1 June 2007.

Nationaal Lucht- en Ruimtevaartlaboratorium, National Aerospace Laboratory NLR

## Nationaal Lucht- en Ruimtevaartlaboratorium

National Aerospace Laboratory NLR

NLR-TP-2007-414

# **Enhanced SAR data compressor for Sentinel-1**

T. Algra and L. Bierens<sup>1</sup>

<sup>1</sup> EONIC B.V.

This report is based on a presentation held on the DASIA 2007 (DAta Systems in Aerospace) Conference, Naples, 29 May - 1 June 2007.

The contents of this report may be cited on condition that full credit is given to NLR and the authors.

This publication has been refereed by the Advisory Committee AEROSPACE SYSTEMS & APPLICATIONS.

Customer National Aerospace Laboratory NLR

Contract number

Owner National Aerospace Laboratory NLR

Division Aerospace Systems & Applications

Distribution Limited

Classification of title Unclassified

November 2007

Approved by:

Author Reviewer Wanaging department

## **Contents**

| ABSTRACT |                                         | 3  |

|----------|-----------------------------------------|----|

| 1        | INTRODUCTION                            | 3  |

| 2        | EFFICIENT ON-BOARD SAR DATA COMPRESSION | 3  |

|          | 2.1 ECBAQ                               | 4  |

|          | Frequency-domain ECBAQ                  | 5  |

| 3        | FFT CO-PROCESSOR ASIC                   | 7  |

| 4        | COMPRESSOR ARCHITECTURE                 | 7  |

| 5        | DEVELOPMENT AND TEST APPROACH           | 10 |

| 6        | CONCLUSIONS                             | 10 |

| 7        | ACKNOWLEDGEMENT                         | 11 |

| 8        | REFERENCES                              | 11 |

### ENHANCED SAR DATA COMPRESSOR FOR SENTINEL-1

Theo Algra (1), Laurens Bierens (2)

- (1) National Aerospace Laboratory NLR, Pbox 90502, 1006 BM Amsterdam, The Netherlands, Email: algra@nlr.nl

- (2) EONIC B.V., Delftechpark 26, 2628 XH Delft, The Netherlands, Email: laurens.bierens@eonic.com

### **ABSTRACT**

This paper presents a new on-board SAR data compressor which outperforms the conventionally used Block Adaptive Quantization (BAQ) compressor. The system applies improved entropy-constrained block adaptive quantization of raw Synthetic Aperture Radar (SAR) data in the frequency domain. For advanced multi-mode satellite SAR instruments, such as the one to be implemented on-board of Sentinel-1, the average compression ratio can be doubled as compared to BAQ. Space borne implementation with a high-speed data throughput is feasible due to the advent of advanced space FPGA's and ASIC's including the powerFFT, a fast FFT-oriented DSP. The complete compressor module can be implemented on a 6U Eurocard that fits in the SAR Electronics System crate of Sentinel-1.

## 1 INTRODUCTION

SAR sensors on-board of remote sensing satellites such as Sentinel-1 generate increasing amounts of data. However, due to download data budget limits, the number of scenes that can be acquired is limited. This calls for the application of on-board data compression.

Block Adaptive Quantization (BAQ) has been applied in some space SAR systems, but this method has a moderate compression ratio. Until so far the rapid developments in terrestrial compression technology of the last decade(s) have not resulted in substantial improvements of on-board SAR data compression systems. This was mainly due to the lack of suitable space-qualified and ultra-complex ASIC's as well as the specific properties of raw SAR data.

This paper presents a new-generation SAR data compressor intended for application on SAR satellites such as Sentinel-1. A high-performance compression method has been developed that operates in the frequency-domain. The FFT-ECBAQ algorithm (Fast Fourier Transform- Entropy Constrained Block Adaptive Quantization) can perform on-the-fly compression with a high-speed data throughput, using an efficient architecture that is based on the fastest space-qualified FPGA and DSP ASIC's available today. One of the key building blocks is the PowerFFT ASIC, currently the fastest DSP for FFT operations. This ASIC will become available in a space-qualified version and its application allows an efficient implementation of the FFT-ECBAQ algorithm involving two-dimensional FFT operation.

The paper successively describes the compression method, the powerFFT device, the architecture of the compressor design, and the development and test approach. The compression ratio and the data throughput are compatible with Sentinel-1 requirements.

## 2 EFFICIENT ON-BOARD SAR DATA COMPRESSION

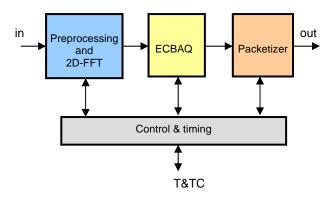

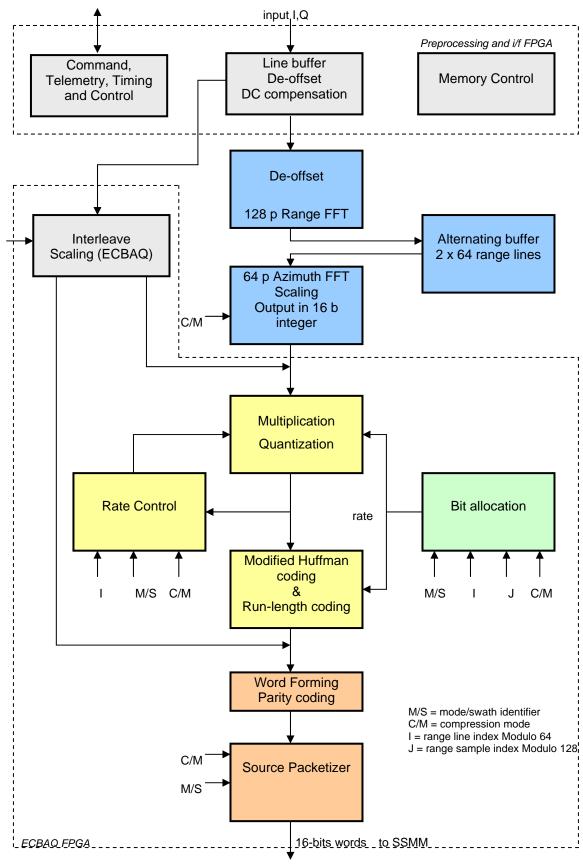

The data compressor consists of four main elements (Fig. 1). The input data stream comprises alternating I and Q samples of 10 bits, with a maximal average rate of ~180 Msamples/s. The Pre-processing and 2D-FFT stage converts the complex input data into the frequency domain. Second, the ECBAQ function performs the actual compression. Third, the encoded data is packed into a CCSDS-compatible source

format. Finally the Control & Timing element provides timing and telemetry signals and allows controlling the compressor by external (tele)commands.

## 2.1 ECBAQ

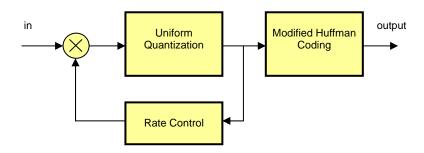

The ECBAQ block diagram is depicted in Fig. 2. In contrast to BAQ, only one quantizer with a uniform transfer function is used. The input data stream is subdivided into blocks of e.g. 256 samples. Before the quantization step, the sample amplitudes are scaled by a factor that is related to the target coding rate. To ensure automatic adaptation to the current signal variance, the scaling factor is updated at each block transition. Finally the quantized samples are entropy encoded.

Fig. 1 FFT-ECBAQ Block diagram

The Signal to Quantization Noise Ratio (SQNR) in the time domain, as a function of the coding rate R, is

$$SONR = 6R - 1.6 dB \tag{1}$$

provided that the optimal step size is used. In other words the standard deviation of the quantizer input  $\sigma_{\rm IN}$  should be equal to an optimal value which has the following relation to the quantization step size S

$$\sigma_{IN} \approx \sigma_{OPT} = 0.24 * 2^R * S \tag{2}$$

However, when  $\sigma_{IN}$  deviates form this ideal value within a range of +/- 3 dB, the distance to the Shannon bound is not really influenced and Eq. 1 remains valid. This allows the implementation of a rate control loop without performance loss and with sufficient instantaneous dynamic range.

The scaling factor update rule uses as an input the percentage of quantized samples with amplitude smaller than the standard deviation set-point. This value is compared to upper and lower limits and results in scaling factor updates by 0, +3 or -3 dB.

In a simplified form the rule can be noted as follows, with  $C_L$  as the fraction of samples with absolute amplitude  $< \sigma_{OPT}$

$$S_{k+1} = S_k - 3 dB \qquad if C_L > 0.84$$

$$S_{k+1} = S_k + 3 dB \qquad if C_L < 0.52$$

$$S_{k+1} = S_k \qquad otherwise$$

(3)

Note that the decoder should perform the same update rule, and hence is able to calculate the scaling factors. Therefore it is not necessary to multiplex the scaling factors with the encoded quantizer output in contrast with an ordinary BAQ compressor.

Fig. 2 ECBAQ block diagram

The quantizer output is efficiently entropy-coded using a Modified Huffman scheme. This means that with an almost negligible performance loss, the maximum code word length will be limited to a practical length of 16 bits.

As compared to BAQ, this method of compression has several benefits:

i) Higher compression ratio; ii) Non-integer coding rates possible; iii) Extended instantaneous dynamic range.

## 2.2 Frequency-domain ECBAQ

Substantial higher compression ratios can be achieved when the ECBAQ operates in the frequency domain. In the digitization section of a SAR system always oversampling is applied in the range dimension. Moreover also in the azimuth dimension oversampling is commonly applied due to the fact that the Doppler processing bandwidth should be significantly smaller than the Pulse Repetition Frequency in order to achieve a sufficient level of image quality. These oversampling factors usually depend on the SAR mode and the subswath and may range from 15% to more than 50%. After 2D-FFT transformation the coefficients which correspond to these oversampling regions can be quantized more coarsely i.e. with a lower bit rate than the other ones.

For speed and memory size reasons the FFT size is limited in practical implementations. In azimuth a 64-points complex FFT is used and in range a 128-points complex FFT. Without the application of overlap & save/add method - which would lead to lower compression gain - these relatively short sizes will cause cross leak noise when the data of the oversampling regions would be omitted, i.e. not encoded and transmitted at all.

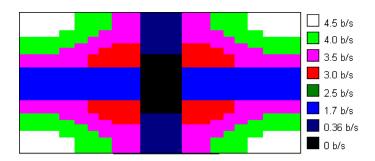

The compression ratio can be further optimized by applying frequency-dependent quantization taking into account the application of apodization functions in SAR image formation processing in the ground segment. In other words for each of the coefficients in the 2D complex sample block of 128 x 64 samples a particular optimal step size is applied with an associated bit rate.

Although the probability density function of the quantization input approximates a Gaussian distribution, the signal includes high peaks due to bright scatterers. This requires a significant extension of the instantaneous dynamic range. ECBAQ allows implementing this requirement without noticeable performance loss.

The use of the rate control loop has several advantages here: i) the scaling factor values do not have to be transmitted; ii) there is no need for a block buffer of 128 complex samples; iii) more important, the loop serves as a low pass filter for the scaling factor updates, suppressing spurious deviations due to high peaks.

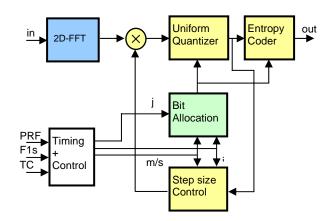

The compressor includes a bit allocation matrix (128 x 64) for each of the possible mode/subswath combinations of the SAR. Fig. 4 shows an example of such a matrix.

The continuously shifting Doppler Centroid in some of the SAR modes can be compensated by the preprocessing stage in order to guarantee correct signal spectrum handling in the azimuth dimension.

Usually the signal level in the range oversampling region is relatively low, which allows further data reduction by the use of runlength encoding.

The results of extensive simulations of the algorithm with real and synthetic SAR data have been reported in Ref. 2.

The reduction in data rate that can be achieved in the case of Sentinel-1 is more than 50% as compared to conventional 4 bits/sample BAQ. Note however that in the Sentinel-1 SAR digitization section probably subsampling will be applied. In that case the rate reduction of FFT-ECBAQ compared to BAQ will be  $\sim$  30%. Compared to time-domain ECBAQ preceded by subsampling, the gain is  $\sim$  20%.

Fig. 3 FFT-ECBAQ Block diagram

Fig. 4 Example of a bit allocation matrix

### 3 FFT CO-PROCESSOR ASIC

Available space-qualified DSP based modules offer a typical computing power of 20 MIPS and more noticeably 20 MFLOPS to 60 MFLOPS. Although it was considered as high a few years ago, future space applications, like raw SAR data compression, radar altimeter processing, optical image processing and even on-board SAR image generation, require a much higher computing power while keeping a substantial level of configurability and flexibility. Therefore a solution based on a specialised processor was favoured by ESA for space applications, the so-called "Fast Fourier Transform Co-Processor" (FFTC).

The design of the FFTC is based on the commercially available PowerFFT<sup>TM</sup> processor IP licensed by ESA from Eonic B.V. The PowerFFT is the world's fastest and most powerful programmable FFT-centric floating-point DSP, able to process 100 million complex samples per second in continuous mode, with a rich set of functionalities for Fast-Fourier Transforms (FFT) computations and FFT-based algorithms, including N-dimensional FFTs, correlations and convolutions. The PowerFFT is a mature ASIC, implemented in numerous military and commercial applications.

The PowerFFT has a 64 bit primary input port, 64 bit primary output port and can execute up to 1K pts FFT or convolution, including windowing, sustained in 10 µs with floating point precision. Four additional I/O ports are available for 4 optional SDRAM (or SRAM) bank extensions for long FFTs, FFT based multi-dimensional algorithms, overlapped algorithms, and (double buffered) corner turning operations.

The flexibility of the memory bank type is guaranteed by using an Address Generator FPGA, which allows cost-effective memory use, easy adoption to addressing schemes used in currently available memories, easy upgrades to larger memories, and specialized memory use for space and military applications. A standard instruction set for the PowerFFT is available for FFT macro-functions ( $\leq$  1M pts. 1D FFT / convolution / correlation,  $\leq$  1K × 1K pts. 2D FFT / convolution / correlation). Upgrade instruction sets can be developed for large (> 1M pts.) 1D, (>1K × 1K pts.) 2D and multi-dimensional FFT-based algorithms (user specific), and other FFT-like Fast Transforms such as Chirped-Z Transform (CZT).

The PowerFFT supports the following standard data formats:

- 32 bit IEEE floating point (parallel or sequential I&Q);

- 32 or 16 bit integer (parallel or sequential I&Q);

and the following specialized data formats:

- 16 or 32 bit sign inverted integer (parallel and sequential I&Q);

- 2×24+9 bits hybrid floating point;

- 2×12+8 bits hybrid floating point.

The PowerFFT runs on a 100 MHz I/O clock maximum, and a 128 MHz internal processing clock. Currently ESA is developing a radiation tolerant version of the PowerFFT and plans to make this FFTC device available to European industry as an ASSP (Application Specific Standard Product) in the course of 2008.

### 4 COMPRESSOR ARCHITECTURE

Fig. 5 shows the system diagram. The pre-processing & interfacing FPGA performs the following functions:

Fig. 5 System diagram

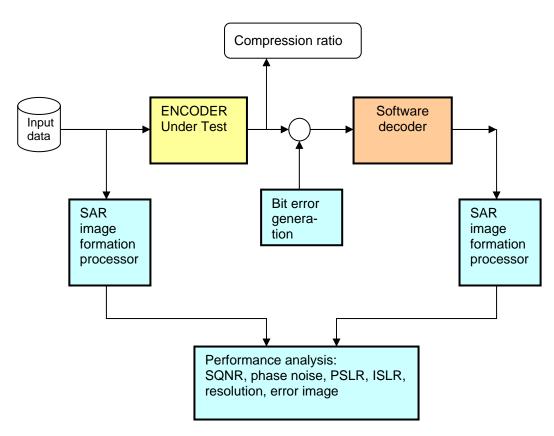

Fig. 6 Test approach

- Echo line buffering to reduce the peak input rate

- Number format conversion (De-offsetting)

- Doppler Centroid compensation (in some modes)

- Memory control for the FFT stage

- Board timing signals generation

- System interface for telemetry and command

The FFT stage uses two powerFFT devices. The first one performs 128 complex points range FFT and the second one 64 complex points azimuth FFT. This 2-dimensional operation requires corner turning of the data. This is accomplished by an alternating buffer of 2 x 64 range lines and a total size of  $\sim$  15MB. The ECBAQ FPGA processes the output of the second powerFFT, consisting of 32-bits complex 2D FFT coefficients, each with a real and an imaginary part.

For the ECBAQ FPGA architecture the following design constraints have been taken into account:

- 1- Platform independency, i.e. the design shall be flexible and upgradeable, and no vendor or platform specific blocks shall be used (dedicated multipliers, memory blocks, etc.);

- 2- Minimize the size of memory resources (LUTs) as much as possible to avoid the necessity of external memory components;

- 3- Effectively the maximum input throughput shall be up to 180 MSPS, but higher throughputs shall be possible in the future.

This FPGA performs the following functions:

- Adaptive Quantization according two-dimensional variable bit allocation

- Entropy coding (Modified Huffman followed by run-length)

- Rate control

- Variable-length to Fixed-length conversion (16 bits words)

- 2-dimensional parity coding for additional protection against transmission bit errors

- Source packetizing

Note that the bit allocation and rate control tables are SAR mode and subswath dependent. The encoded data of each 2D FFT block results in a self-contained CCSDS source packet. In other words each packet can completely be decoded without the need for information from previous packets. The FFT-ECBAQ is able to switch to time-domain compression. In that case the FFT stage is bypassed and the ECBAQ algorithm is performed in the time-domain.

The parity coding function provides additional protection against transmission bit errors. Although the probability of a bit error is small (10<sup>-9</sup>), the effect may be that a (large) part of 128x64 samples block is erroneously decoded due to the loss of synchronization in the variable-length coding stream. With parity coding the resulting bit error probability is reduced to less than 10<sup>-11</sup> at the expense of about 1% coding rate increase.

The ECBAQ implementation fits in a medium-sized space qualified FPGA (Actel RTAX2000). The complete compressor module can be implemented on a 6U Eurocard that fits in the SAR Electronics System crate. The output data is directly relayed to the on-board mass memory using high speed data links.

### 5 DEVELOPMENT AND TEST APPROACH

Fig. 6 shows the basic test setup. The encoder is tested with real and synthetic raw SAR data. The original data as well as the decompressed data is processed into single-look complex slant-range images with equal processing parameters. The two images are compared to derive the compression noise level and to evaluate the image quality. The development comprises the following phases.

First a software-based encoder/decoder pair is developed and tested against the specifications. Image quality, compression ratio, and estimated on-board data speed are the verification requirements. In the next phase the ECBAQ part of the encoder is replaced by a VHDL simulation of the ECBAQ FPGA. Finally, the software encoder is completely replaced by the hardware model.

Obviously, if it is assured that hardware and software encoders have exactly the same data handling down to bit level, that in practice the verification can be limited in most cases to comparing encoder output files.

The test setup includes a feature to generate random bit errors in the compressed data in order to verify the built-in error correction mechanism.

### 6 CONCLUSIONS

For the compression of raw data from multi-mode SAR instruments, frequency-domain entropy-constrained BAQ (FFT-ECBAQ) is an attractive option. The average compression ratio is more than twice that of BAQ with the same image quality. The implementation on-board of satellites is feasible due to the availability of the PowerFFT, a fast FFT-oriented DSP ASIC, which is currently being space-qualified.

It is recommended to verify the design by implementation and test with real and simulated SAR data, in particular in the Sentinel-1 interferometric wide swath mode which applies a progressive scan technique.

## 7 ACKNOWLEDGEMENT

The results presented in this paper are based on the output of ESA contract 18992/05/NL/MV and NIVR contract 61524EO.

## 8 REFERENCES

- 1. Sentinel-team, "GMES Sentinel-1 System requirements Document", S1-RS-ESA-SY-0001, issue 2, revision 0, ESTEC, 20 April 2006

- T. Algra and L. Bierens, "Frequency domain raw SAR data compression for multi-mode satellite SAR instruments", Proc. EUSAR 2006

- Algra, T., L. Bierens, Advanced on-board SAR data compression FFT-ECBAQ performance and quality test results, NLR-CR-2006-87, ESA contract 18992/05/NL/MV, 2006

- 4. System Specifications and Performance Analysis, v1.0, Technical Note PEP05-TN-001, EONIC/NLR, February 2007

- 5. Architecture and FPGA Design, v1.1, Technical Note PEP05-TN-002, EONIC/NLR, February 2007

- FFT-ECBAQ Unit Tester Specification, v1.0, Technical Note PEP05-TN-003, EONIC/NLR, March 2007

- 7. Space Qualifiability Assessment, v1.0, Technical Note PEP05-TN-004, EONIC/NLR, (in progress)